# CIRCUITOS DIGITALES

- Conceptos preliminares

- Familias lógicas

- Topologías

- Compuertas

- Flip Flops

- Osciladores

- Memorias

# Conceptos preliminares

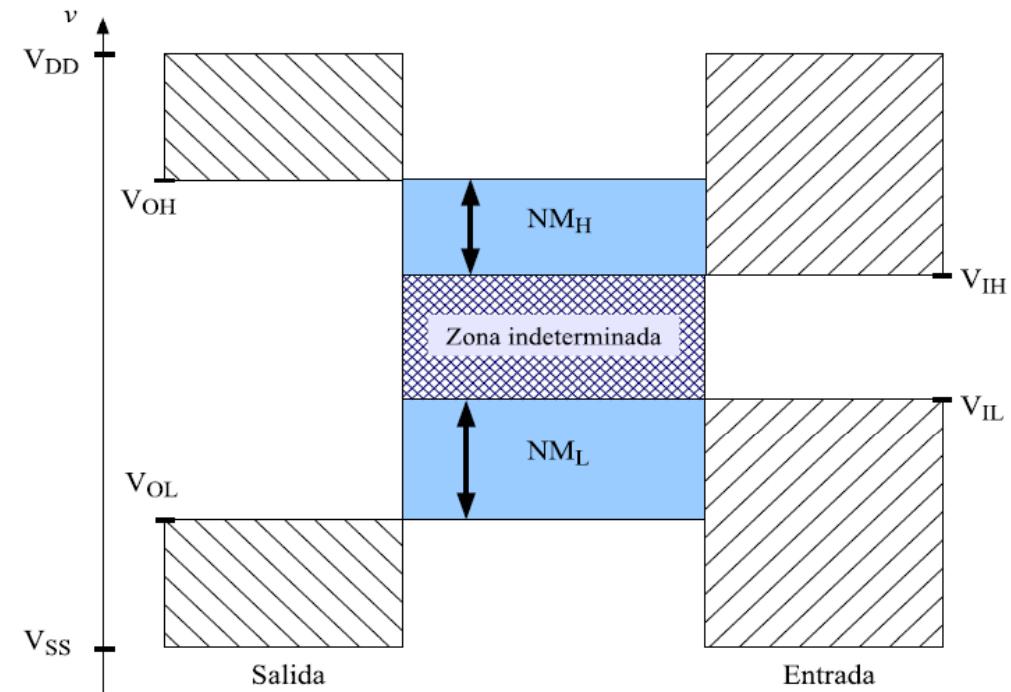

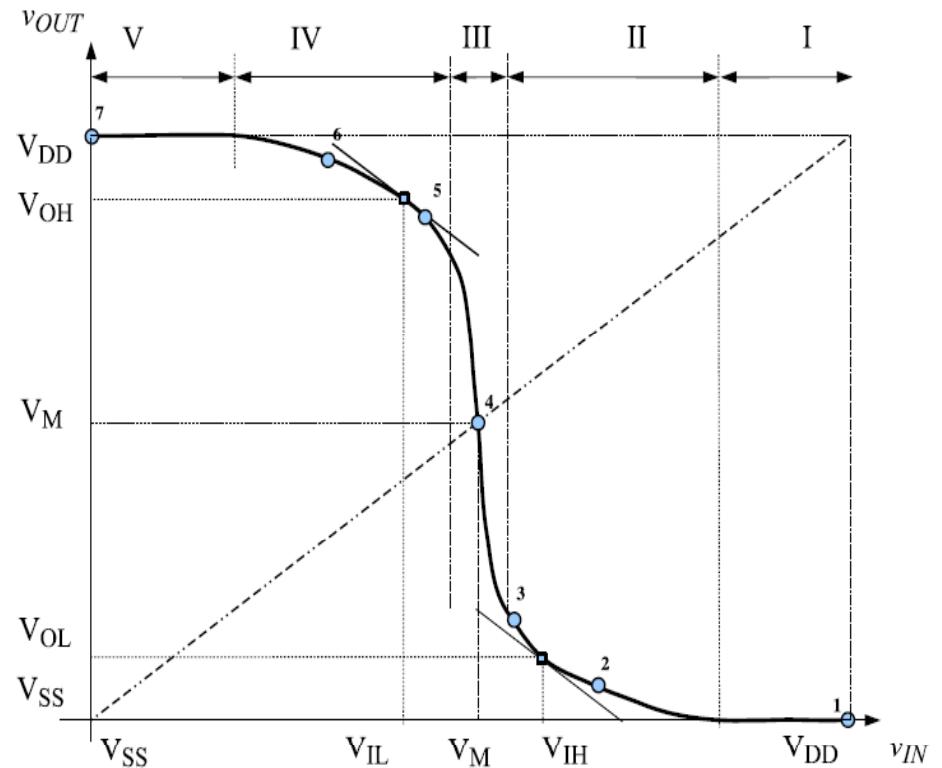

- **Máximo nivel de tensión de entrada para un nivel lógico bajo  $V_{IL}$ :** es el máximo nivel de tensión en la entrada que es interpretado como un nivel lógico bajo.

- **Mínimo nivel de tensión de entrada para un nivel lógico alto  $V_{IH}$ :** es el mínimo nivel de tensión en la entrada que es interpretado como un nivel lógico alto.

- **Máximo nivel de tensión de salida para un nivel lógico bajo  $V_{OL}$ :** es el máximo nivel de tensión a la salida que la compuerta produce como nivel lógico bajo.

- **Mínimo nivel de tensión de salida para un nivel lógico alto  $V_{OH}$ :** es el mínimo nivel de tensión de salida que es interpretado como un nivel lógico alto.

# Conceptos preliminares

- **Margen de ruido:** indica la inmunidad de un sistema lógico de soportar la presencia de ruidos eléctricos sin cambiar de estado.

$$NM_L \triangleq V_{IL} - V_{OL}$$

$$NM_H \triangleq V_{OH} - V_{IH}$$

compuerta ideal

$$V_{OH} = V_{DD}, V_{OL} = V_{SS}$$

$$V_{IH} = V_{IL} = V_{DD}/2$$

$$NM_L = NM_H = V_{DD}/2$$

# Conceptos preliminares

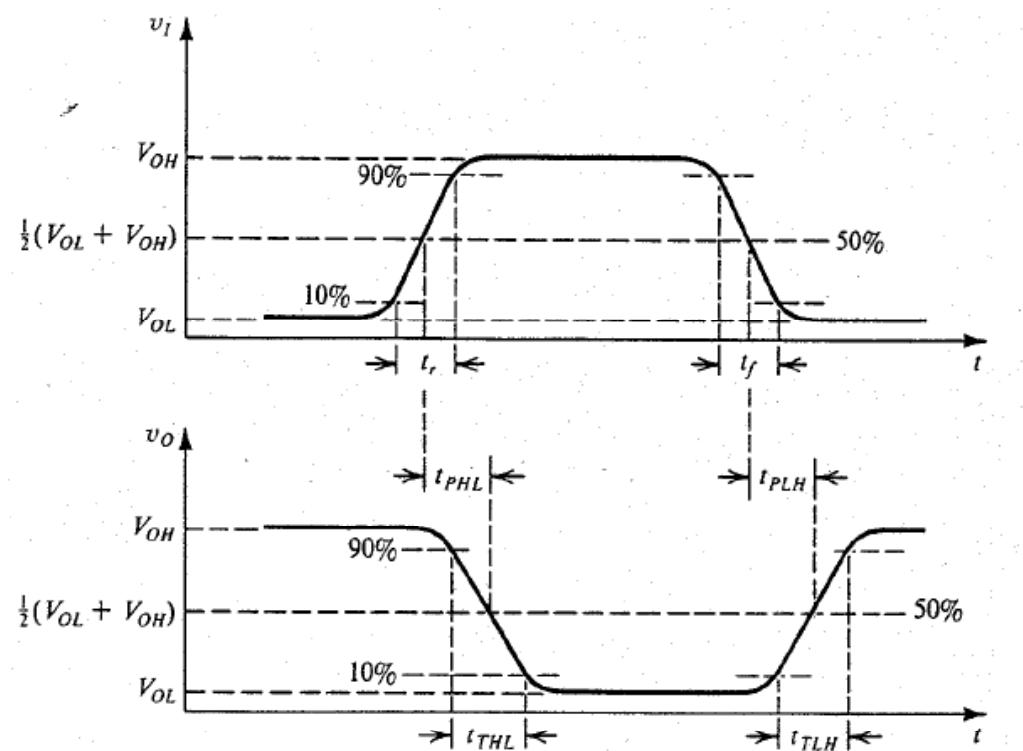

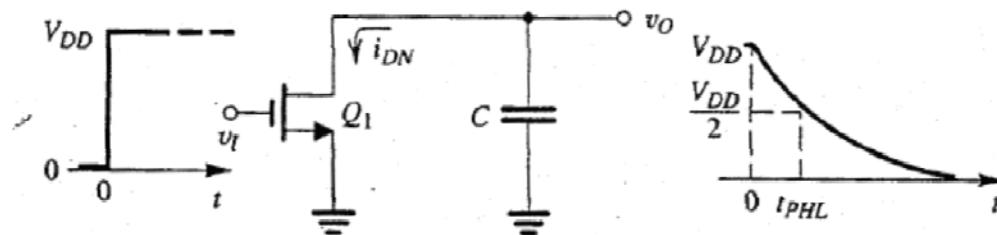

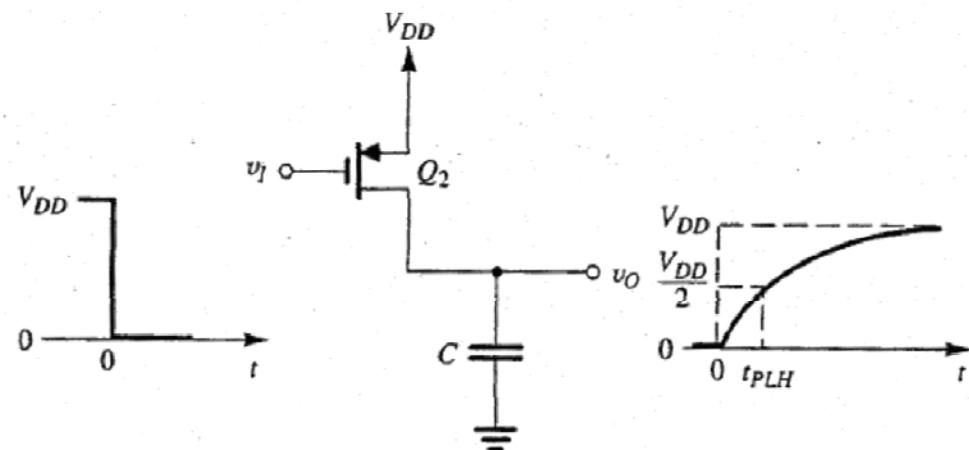

- **Retardo de Propagación**

- La performance de una lógica se define por el tiempo de propagación de un inversor básico.

$$t_P \equiv \frac{1}{2}(t_{PLH} + t_{PHL})$$

Cuanto menor es  $t_P$ , mayor es la frecuencia a la cual puede operar el circuito digital

# Conceptos preliminares

- **Cargabilidad**

- **Fan-In:** consumo relativo de la entrada de un circuito lógico, referido a una celda unidad. Va en función de cómo se distribuye internamente la señal de entrada.

- **Fan-Out:** capacidad de manejo que tiene una salida de un circuito lógico, referido a una celda unidad.

# Conceptos preliminares

- **Disipación de Potencia**

- Disipación Estática

- Ocurre cuando la lógica se encuentra en un estado estable, sin cambios en los niveles lógicos.

- Disipación Dinámica

- Ocurre cuando la lógica conmuta sus niveles lógicos. Esto provoca demandas de corriente adicional para realizar el cambio de estado lógico.

- En todo cambio de estado lógico se encuentra involucrada la carga y/o descarga de capacidades del circuito, ya sean propias de los componentes o parásitas.

$$P_D = fCV_{DD}^2$$

# Familias lógicas

- CMOS (Complementary Metal Oxide Silicon)

- Mayormente utilizada hoy en día. Procesos actuales: 32nm (Core-i5, 3.73Ghz, 2.6Ghz FSB)

- TTL (Transistor – Transistor Logic)

- TTL clásica

- L (Low)

- LS (Low Schottky)

- S (Schottky)

- F (Fast)

- HC (High CMOS)

- HCT (Hight CMOS TTL)

- ACT (Advanced CMOS TTL)

- ECL (Emitter Coupled Logic) → Muy alta velocidad

- DTL (Diode Transistor Logic) RTL (Resistor Transistor Logic) → Obsoletas

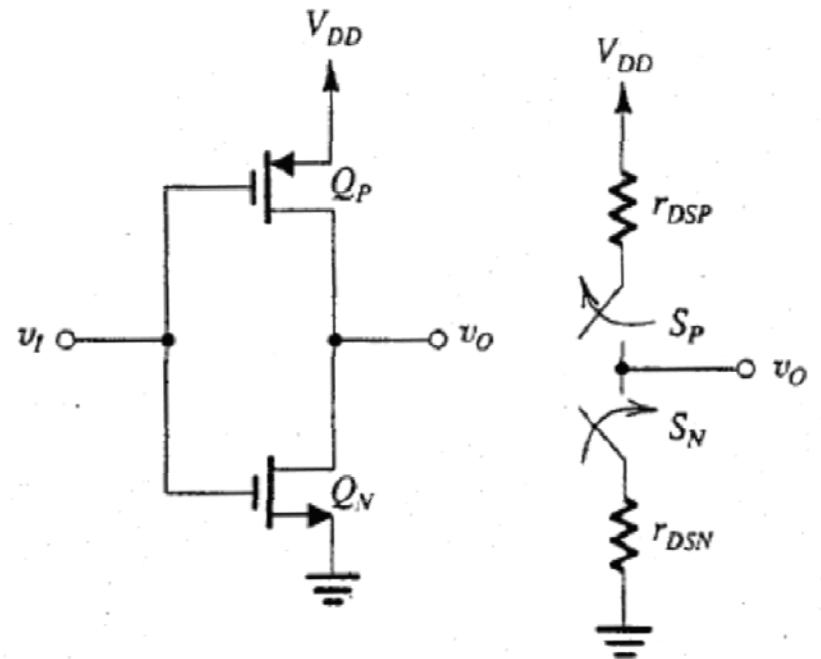

# Inversor CMOS

- Cada transistor se lo puede modelar como una llave con una resistencia de canal:

$$r_{DSN} = 1 \left/ \left[ k'_n \left( \frac{W}{L} \right)_n (V_{DD} - V_t) \right] \right.$$

$$r_{DSP} = 1 \left/ \left[ k'_p \left( \frac{W}{L} \right)_p (V_{DD} - V_t) \right] \right.$$

$$|v_{DS}| = 0$$

- Con  $v_i = 0 \rightarrow v_o = V_{DD}$  a través de la resistencia de  $Q_P$ .

- Con  $v_i = V_{DD} \rightarrow v_o = 0$  a través de la resistencia de  $Q_N$ .

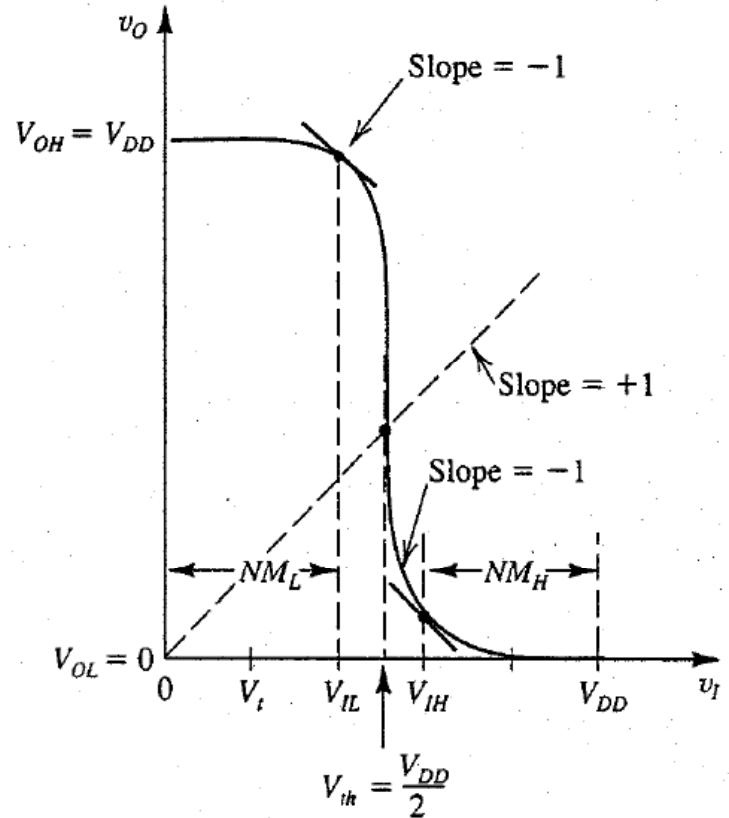

# Curva de transferencia

- Los transistores  $Q_P$  y  $Q_N$  tienen las dimensiones tales que el umbral de comutación se ubica en  $V_{DD}/2$ .

$$V_{th} = \frac{V_{DD} - |V_{tp}| + \sqrt{k_n/k_p} V_{tn}}{1 + \sqrt{k_n/k_p}}$$

$$k_n = k'_n(W/L)_n \text{ and } k_p = k'_p(W/L)_p$$

$$V_{tn} = |V_{tp}|, V_{th} = V_{DD}/2$$

$$k_n = k_p \quad k'_n(W/L)_n = k'_p(W/L)_p$$

$$\left(\frac{W}{L}\right)_p = \frac{\mu_n}{\mu_p} \left(\frac{W}{L}\right)_n$$

Introducción a la Electrónica

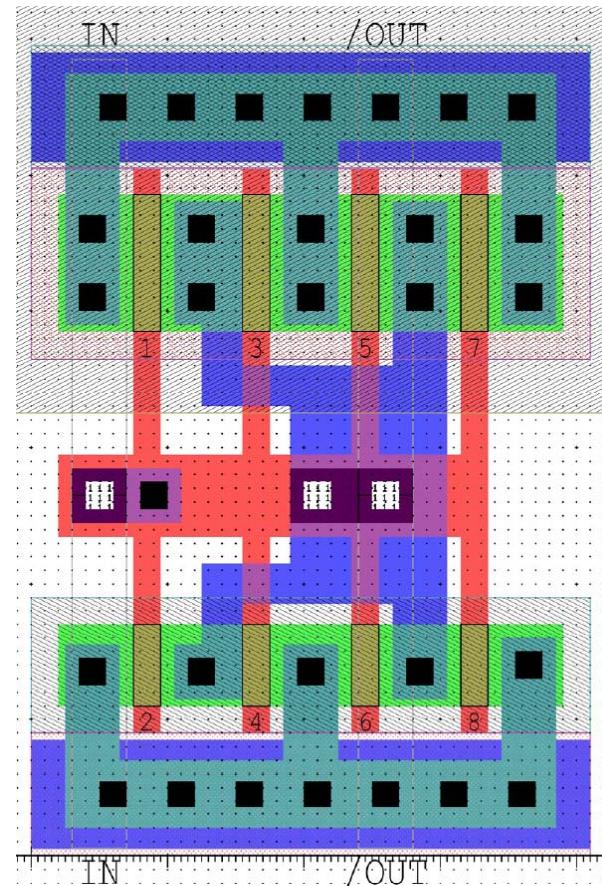

# Curva de transferencia

- Para lograr simetría en la curva de transferencia, debido a la diferencia en la movilidad de los portadores n y p, es necesario diseñar los transistores p con un ancho (W) mayor que los del tipo n.

- El largo del canal (L) habitualmente es fijo y está dado por el tamaño mínimo que soporta el proceso.

Introducción a la Electrónica

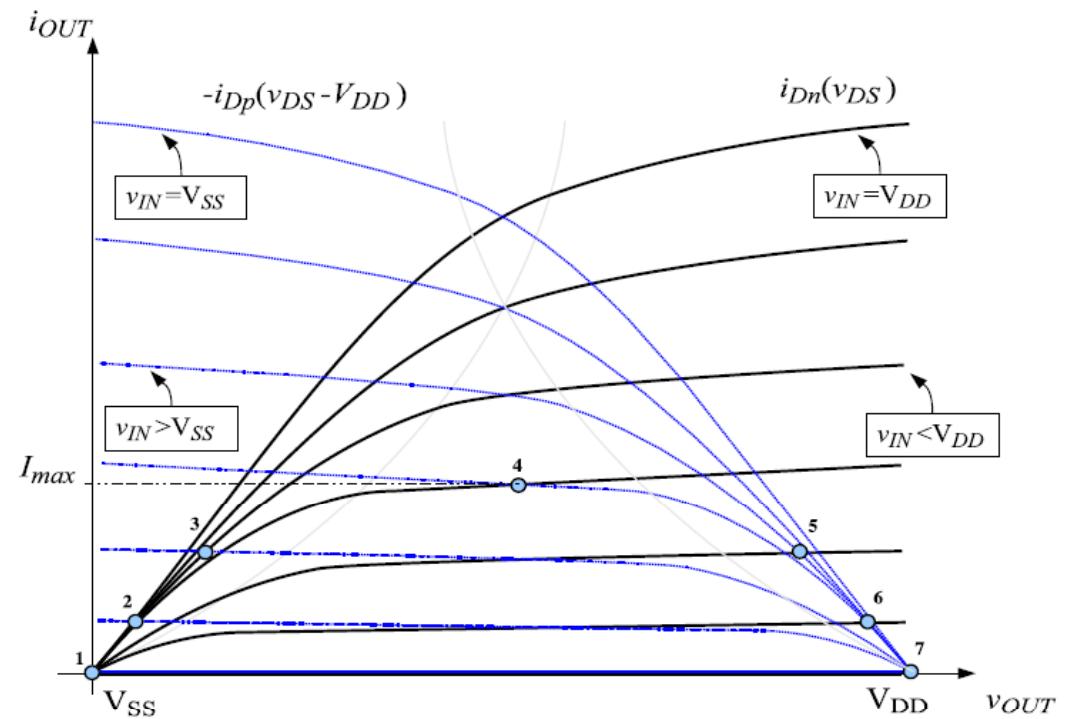

# Puntos de Trabajo

- En función de la tensión de salida del inversor, la ubicación del punto de trabajo de ambos transistores (P y N) vendrá dado por las gráficas del dibujo.

# Puntos de Trabajo

- V. NMOS en corte y PMOS en triodo

- IV. NMOS en saturación y PMOS en triodo

- III. NMOS en saturación y PMOS en saturación

- II. NMOS en triodo y PMOS en saturación

- I. NMOS en triodo y PMOS en corte

# Operación Dinámica

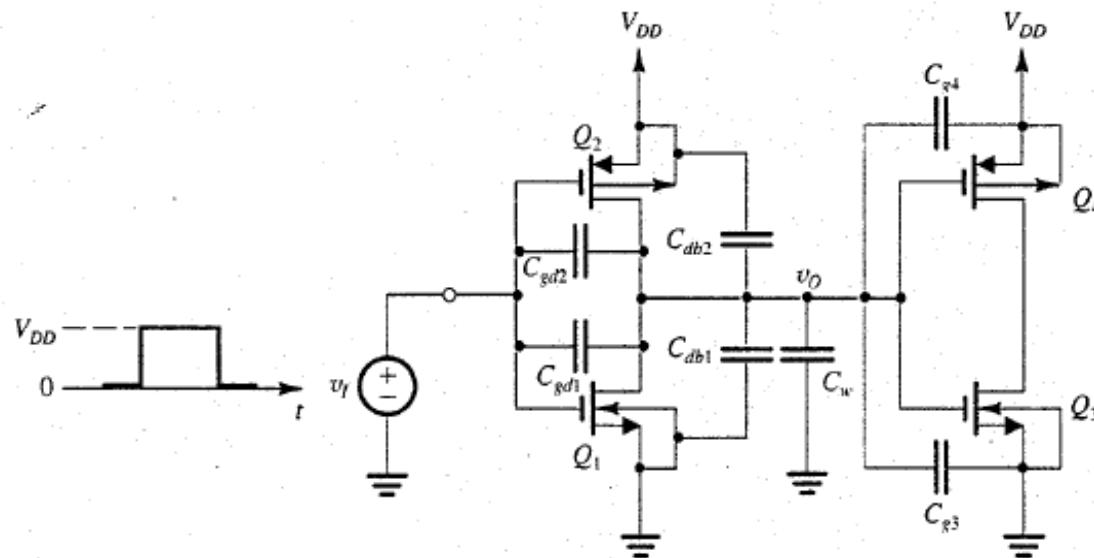

- Todas las capacidades internas de los transistores forman parte en el proceso de conmutación de niveles en el inversor.

# Operación Dinámica

$$C = 2C_{gd1} + 2C_{gd2} + C_{db1} + C_{db2} + C_{g3} + C_{g4} + C_w$$

(a)

$$t_{PHL} \cong \frac{1.7 C}{k'_n \left(\frac{W}{L}\right)_n V_{DD}}$$

$$t_{PLH} \cong \frac{1.7 C}{k'_p \left(\frac{W}{L}\right)_p V_{DD}}$$

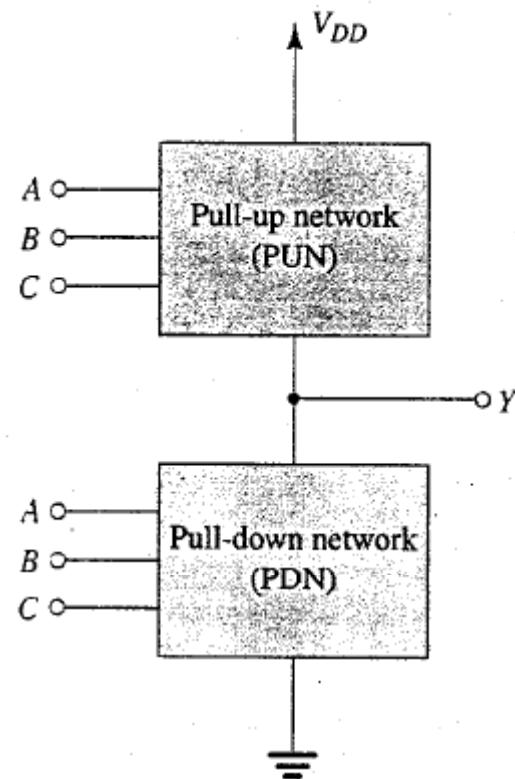

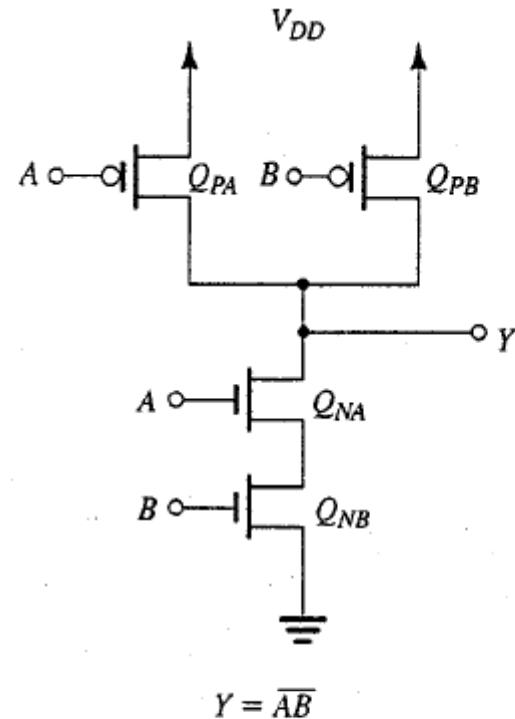

# Compuertas CMOS

- Estructura básica de una compuerta

- Red de Pull-up que fija el nivel alto.

Transistores PMOS

- Red de Pull-down que fija el nivel bajo.

Transistores NMOS

- En base a la función lógica a implementar, cada red tendrá una topología determinada.

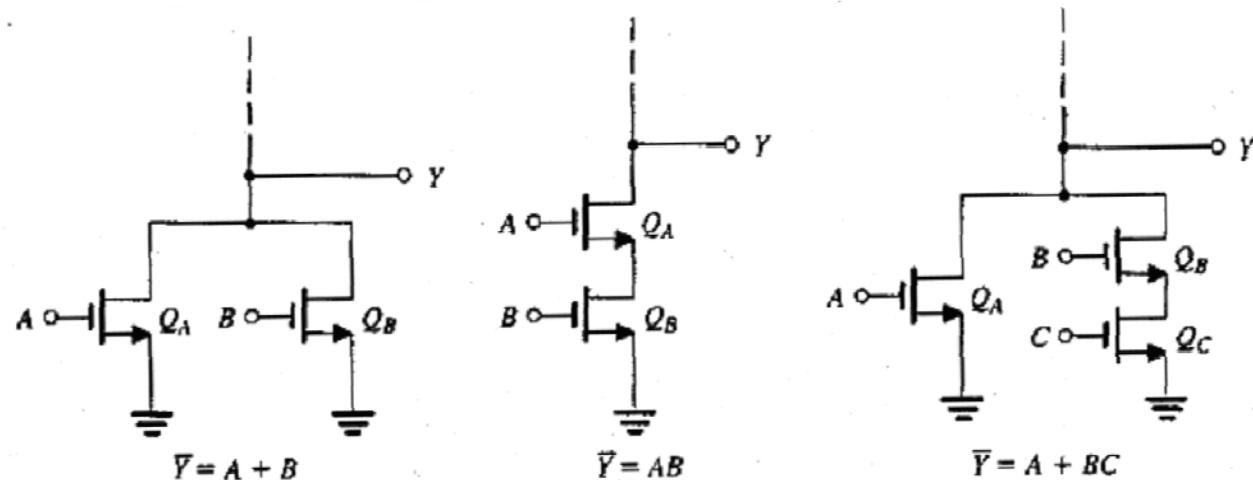

# Compuertas CMOS

- Ejemplos de redes Pull-down

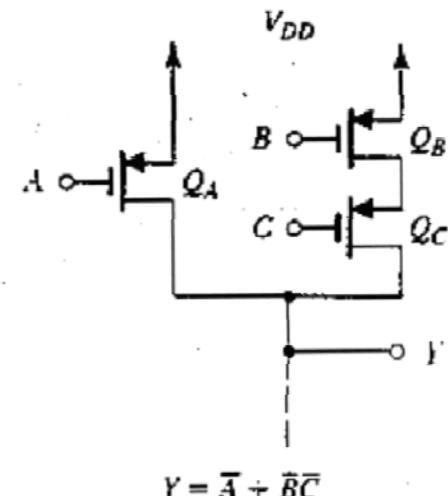

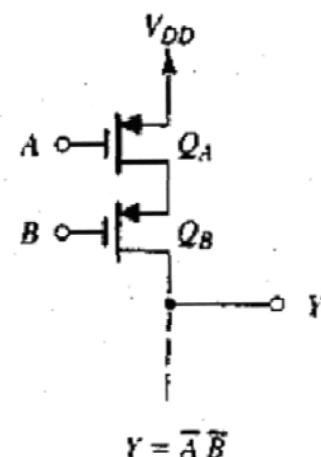

# Compuertas CMOS

- Ejemplos de redes Pull-up

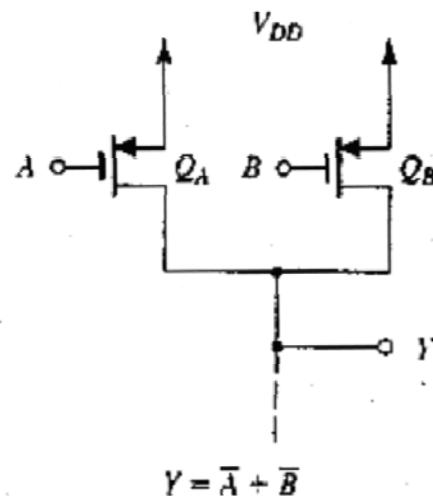

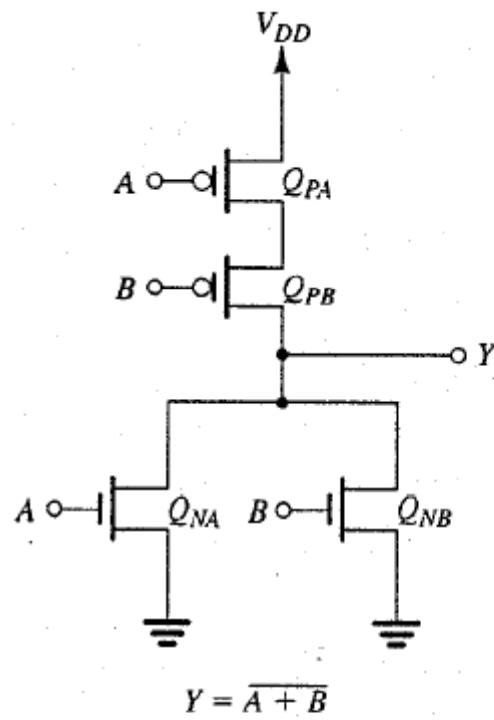

# Ejemplos compuertas CMOS

Fig. 13.12 A two-input CMOS NOR gate.

Fig. 13.13 A two-input CMOS NAND gate.

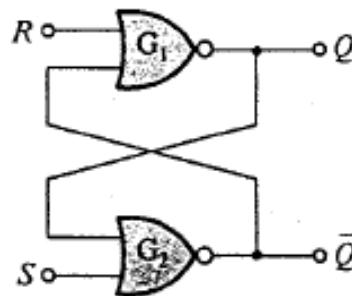

# Circuitos secuenciales

- Son aquellos, en los cuales el estado lógico de las salidas depende no solamente del valor de las entradas, sino también del historial.

- Evolucionan de manera asincrónica o sincrónica con una señal de reloj.

- La manera de dotar a estos circuitos con memoria es a través de una realimentación positiva, de manera de lograr un circuito biestable capaz de almacenar 2 estados lógicos posibles.

- Ejemplos

- Flip flops

- Contadores

- Memorias SRAM

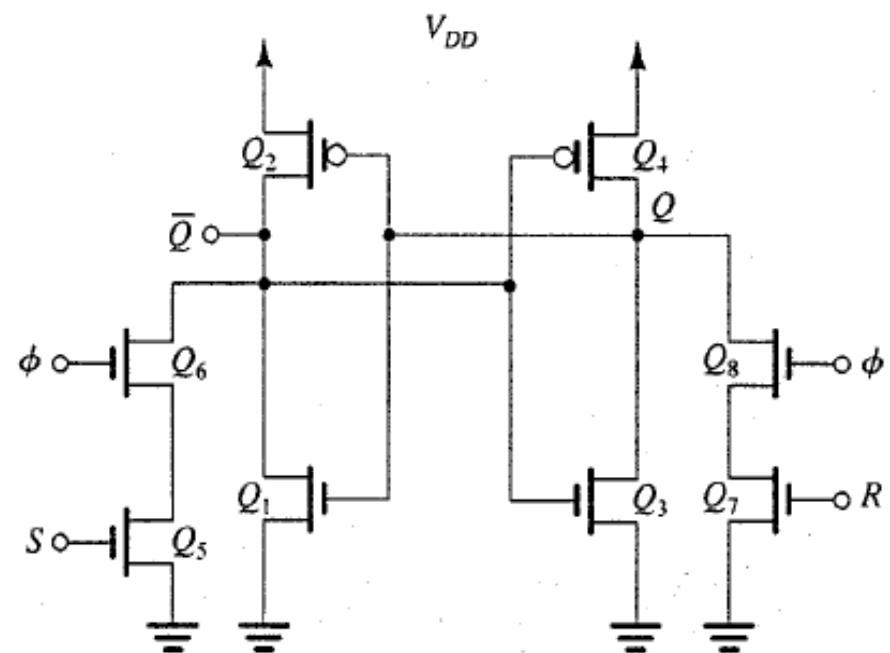

# Flip Flop CMOS

- Flip Flop RS

| R | S | $Q_{n+1}$ |

|---|---|-----------|

| 0 | 0 | $Q_n$     |

| 0 | 1 | 1         |

| 1 | 0 | 0         |

| 1 | 1 | Not used  |

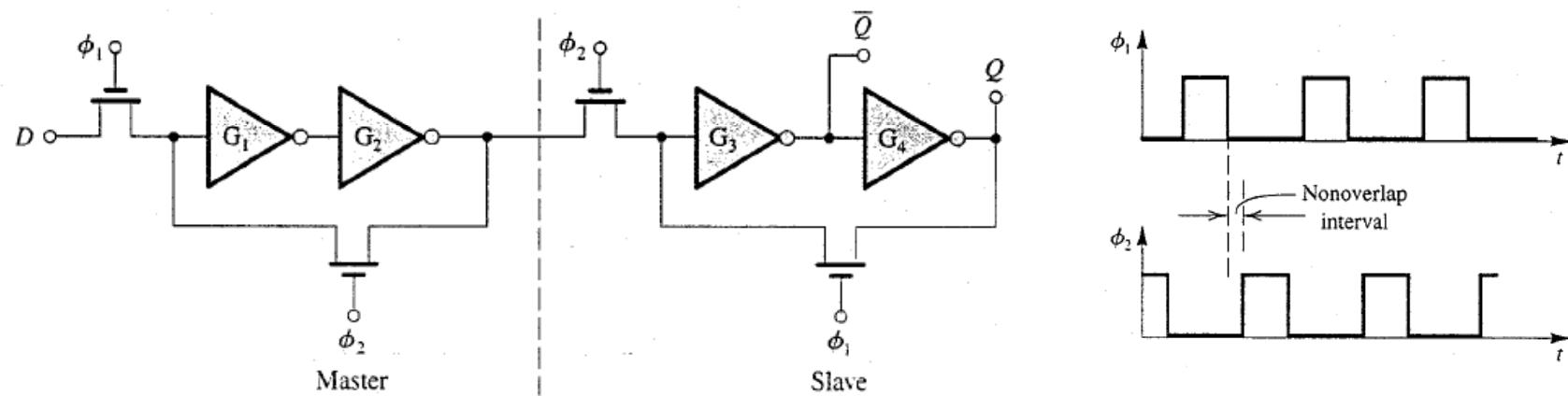

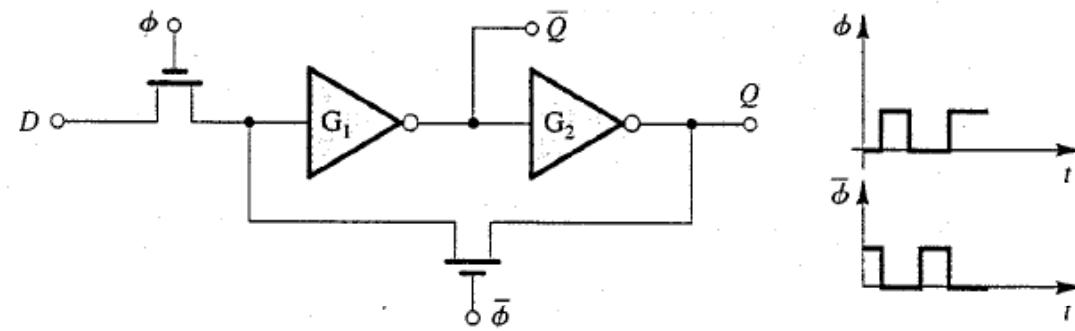

# Flip Flop CMOS

- Flip Flop D (latch)

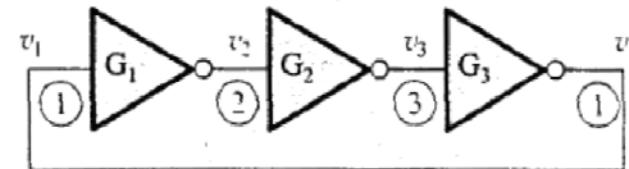

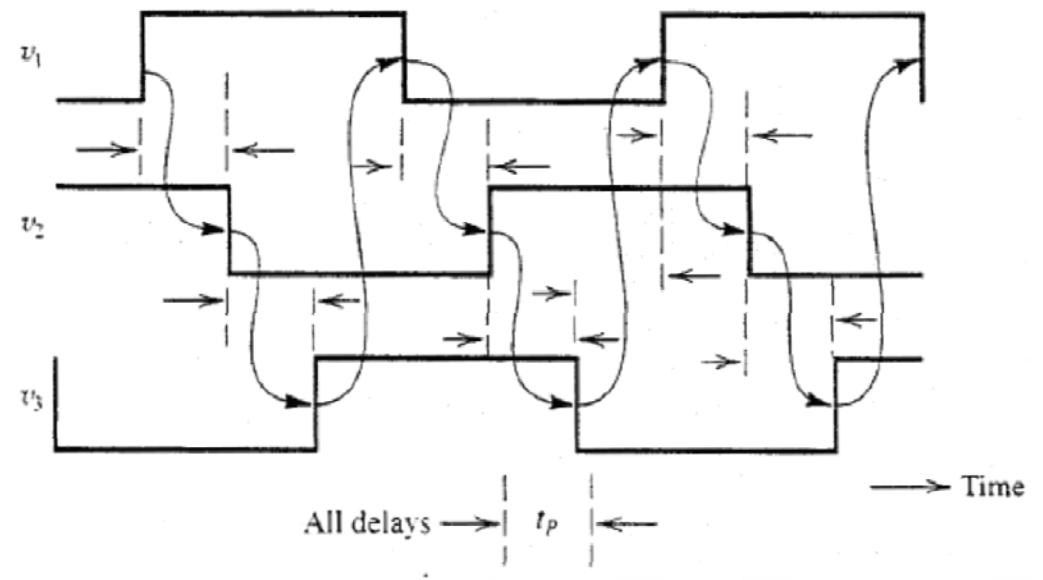

# Ring Oscillator

- Número impar de inversiones

- Se lo suele emplear como parámetro de medición de la velocidad de una familia lógica.

- Tiempo de propagación total:

$$6t_P$$

(a)

Introducción a la Electrónica

# Memorias

- RAM (Random Access Memory)

- Lectura/escritura

- Estática

- Dinámica

- Alta integración

- ROM (Read Only Memory)

- Solamente lectura

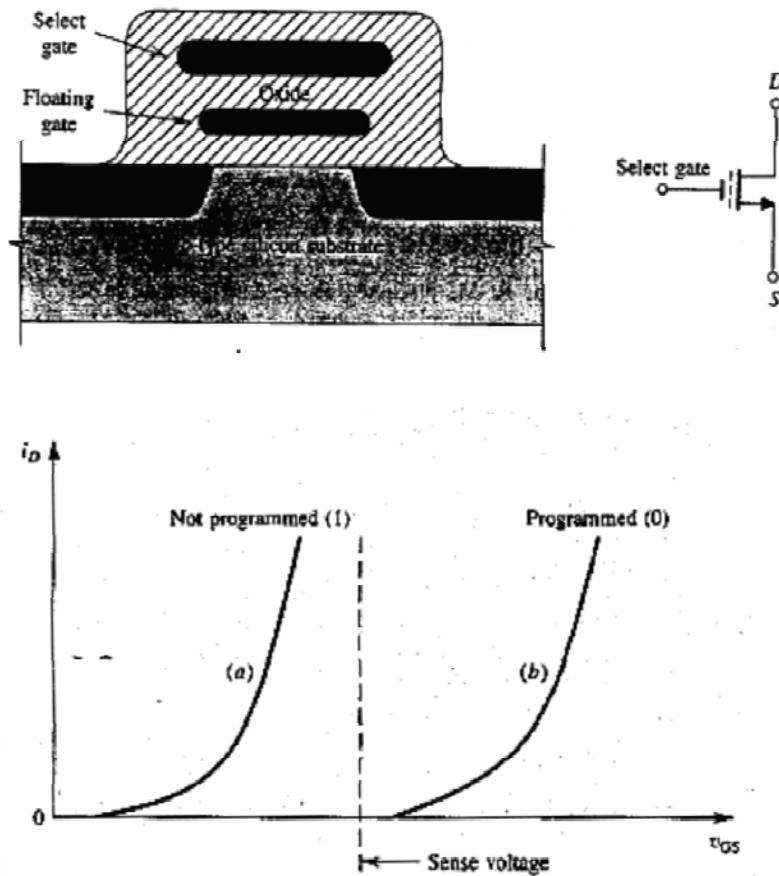

- Eproms

- Eeproms

- Flash

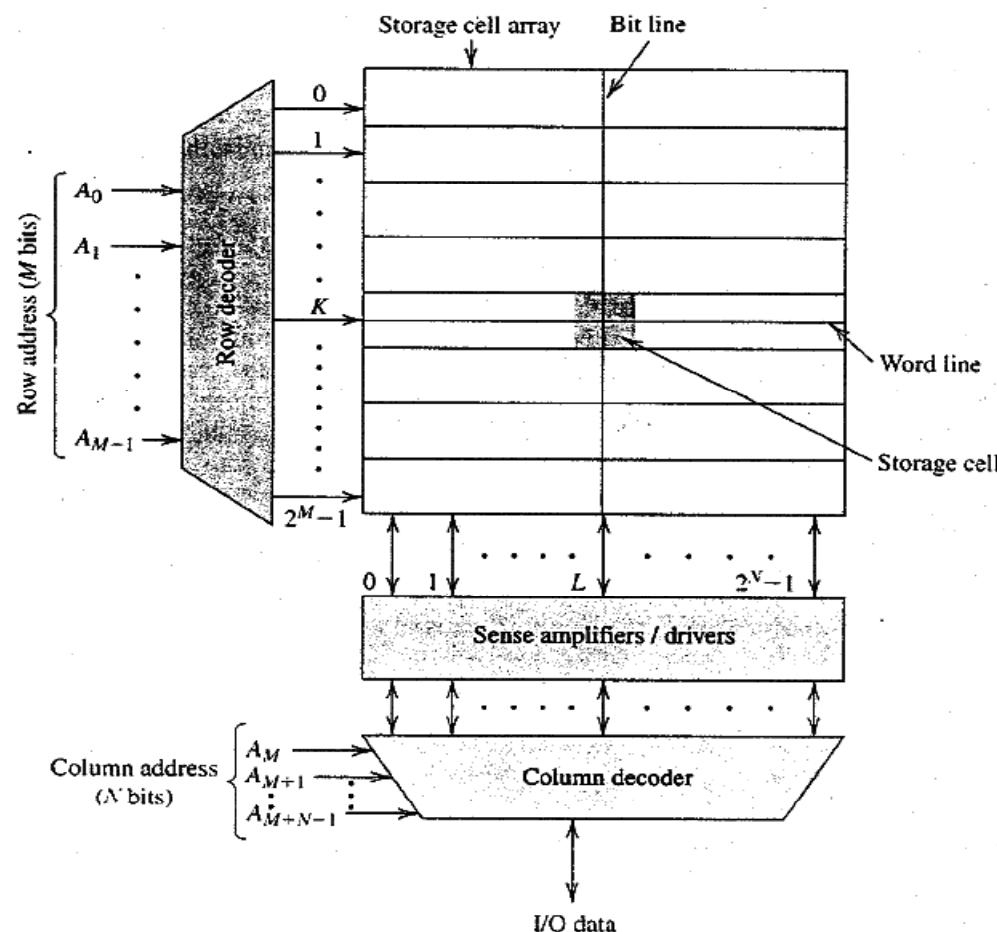

# Memorias

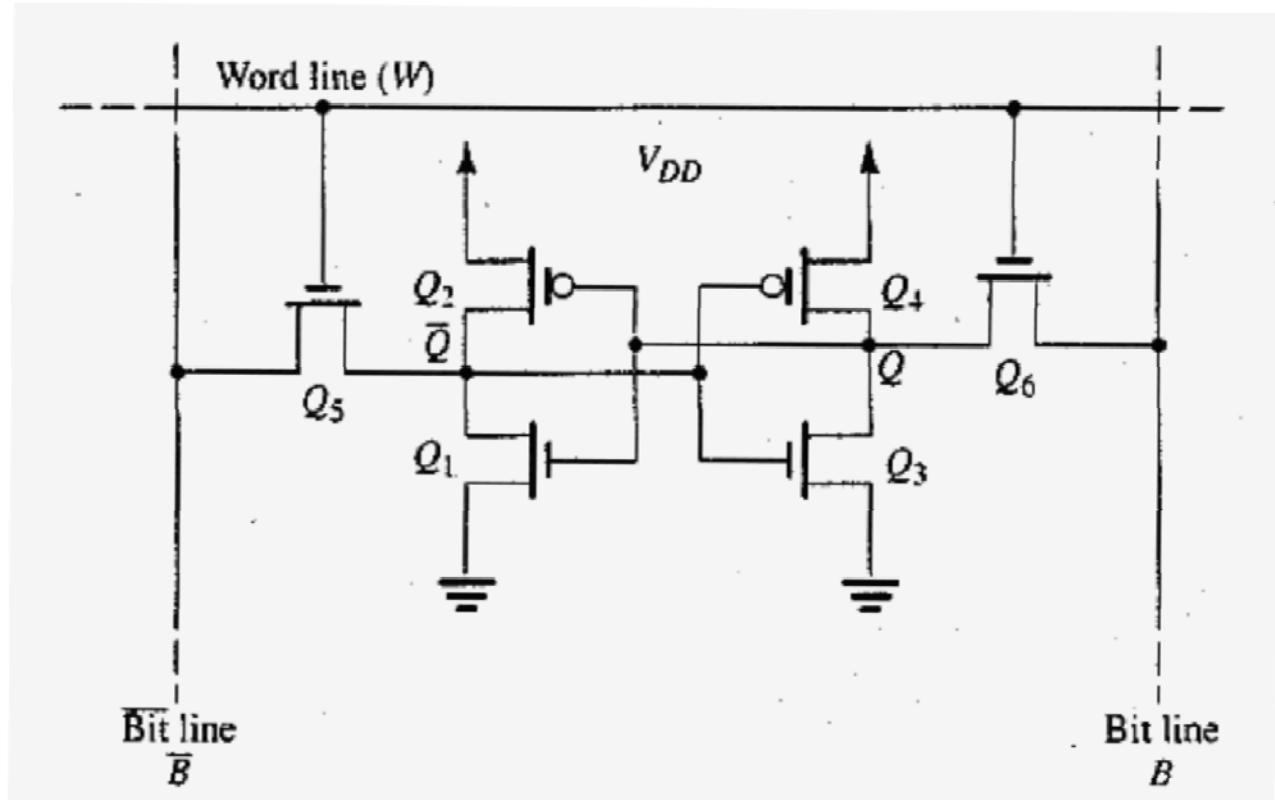

# SRAM

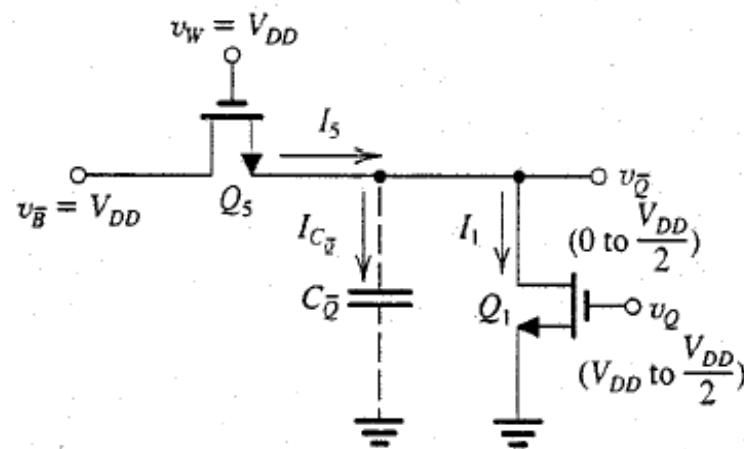

- Las capacidades de las líneas  $B$  y  $/B$  se precargan a  $V_{DD}/2$ .

- En función del valor almacenado, los transistores  $Q_5$  y  $Q_6$  fijarán los niveles lógicos de  $B$  y  $/B$ .

- La tensión diferencial entre  $B$  y  $/B$  determina el valor del Bit ( $> 0,2V$ )

# Memorias

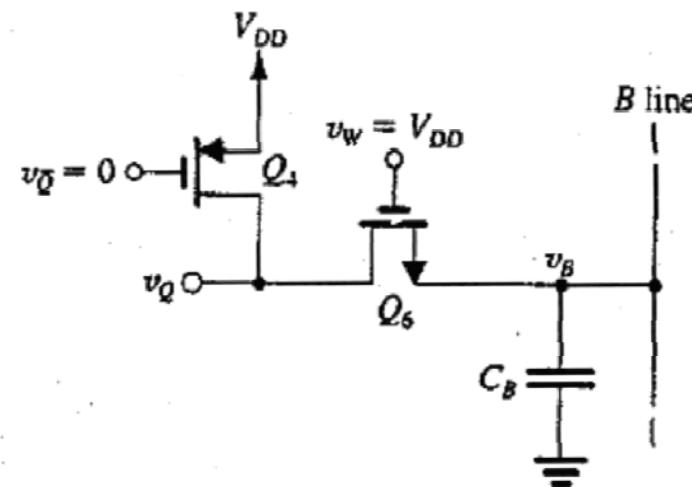

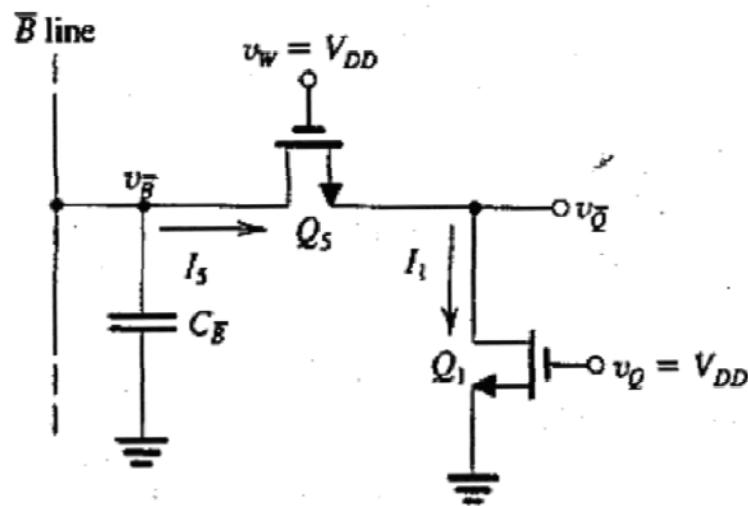

- Lectura de un ‘1’ en una SRAM

# Memorias

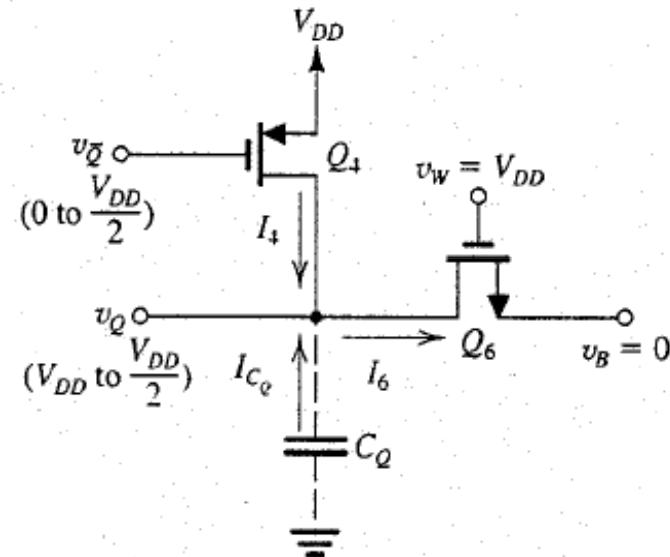

- Escritura de un '0' en una SRAM

- B se coloca en '0' y /B en '1'

# Memorias

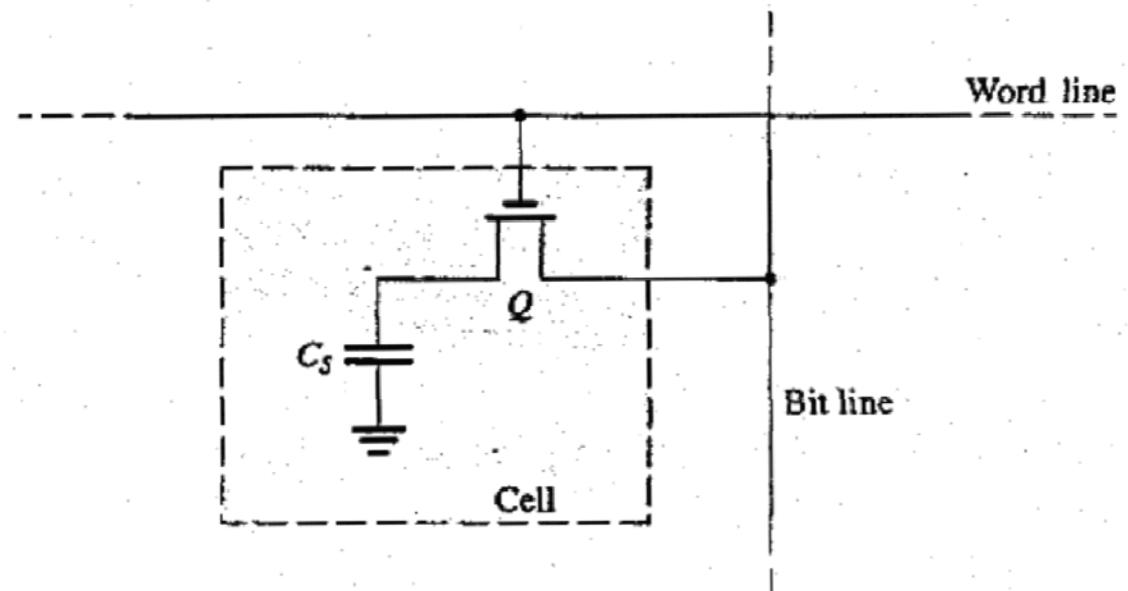

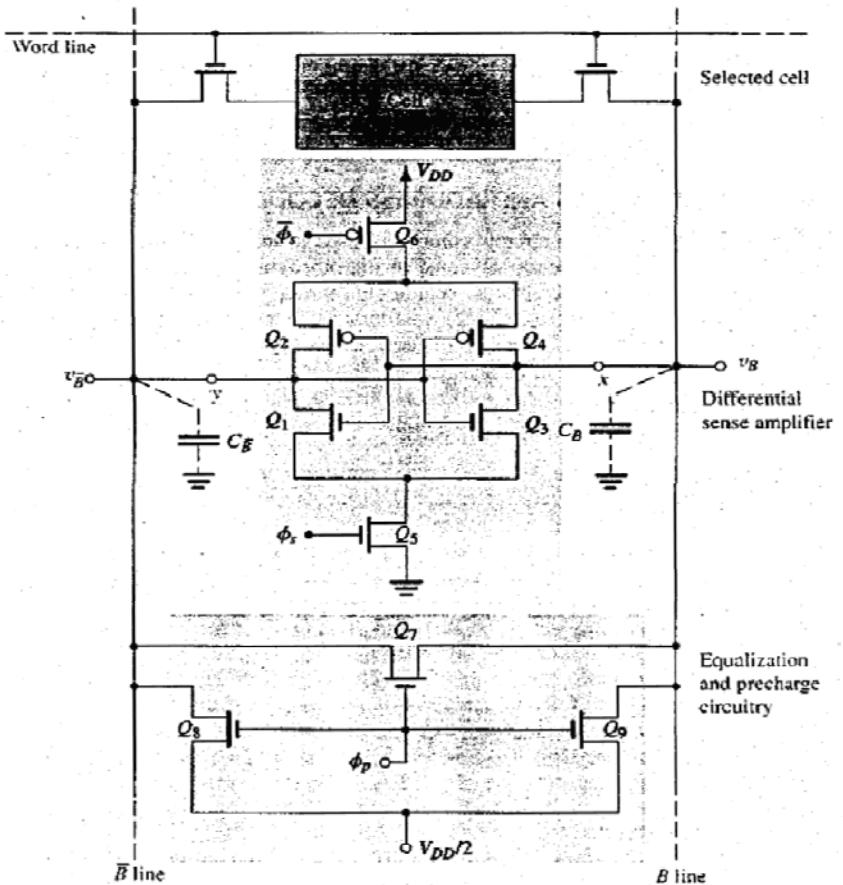

- **Memoria Dinámica**

- Se refresca cada 5-10mSeg

- La lectura es un proceso destructivo. Se precarga a  $V_{DD}/2$  el bus.

- $C_S \approx C_B/50$

- $\Delta V \approx 30\text{mV}$

# Memorias

- **Estructura Interna**

- El Sense Amplifier es un circuito realimentado que al activarse amplifica la pequeña tensión presente en el bus y la lleva a los valores lógicos adecuados.

- En una DRAM se aprovecha la lectura para hacer un ciclo de refresco.

- El bloque de precarga lleva el bus a  $V_{DD}/2$  antes de una lectura.

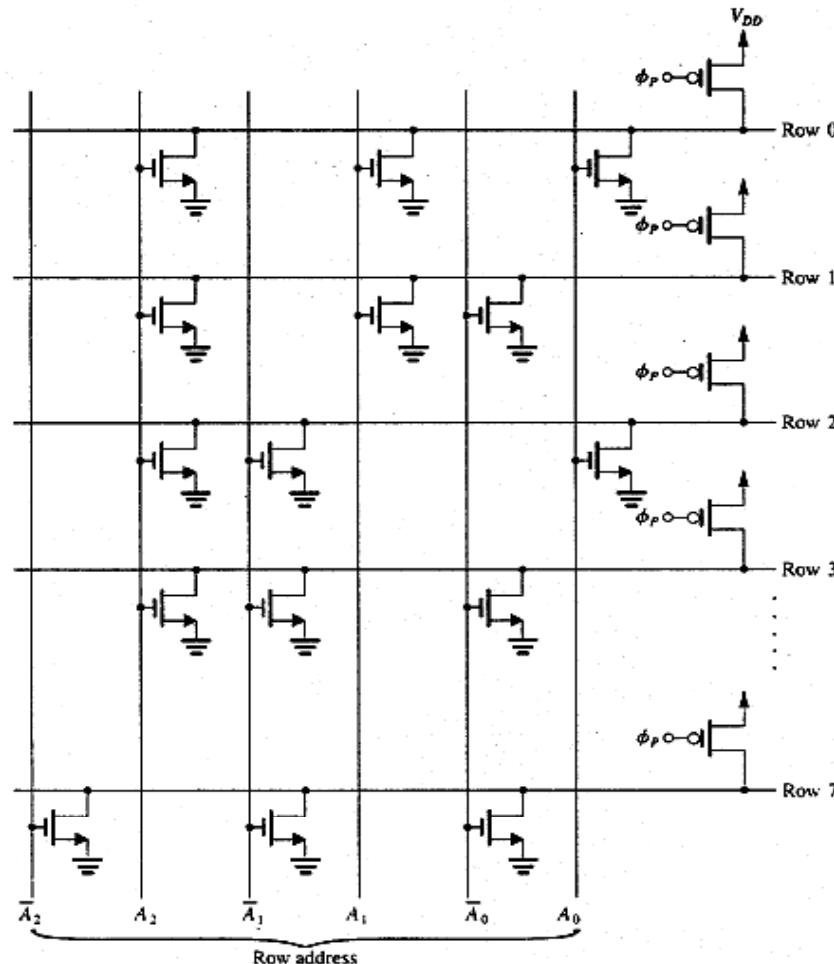

# Decodificadores

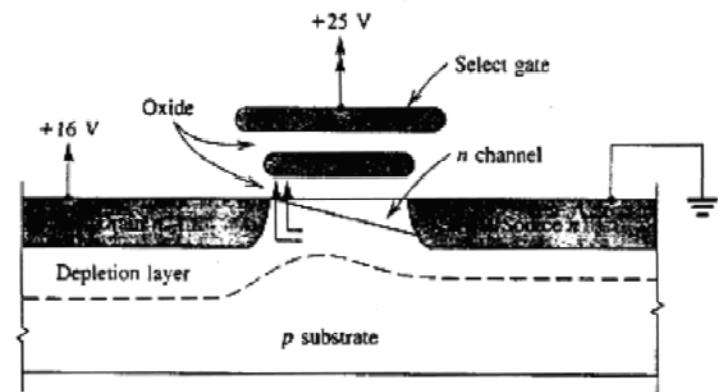

# Memorias Eprom

# Contadores

- Circuito secuencial

- Avanzan con una señal de reloj

- Cuentan en Binario o Decimal

- Implementados con Flip-Flops

- Suelen tener posibilidad de Reset o Carga

- Asincrónicos

- Sincrónicos

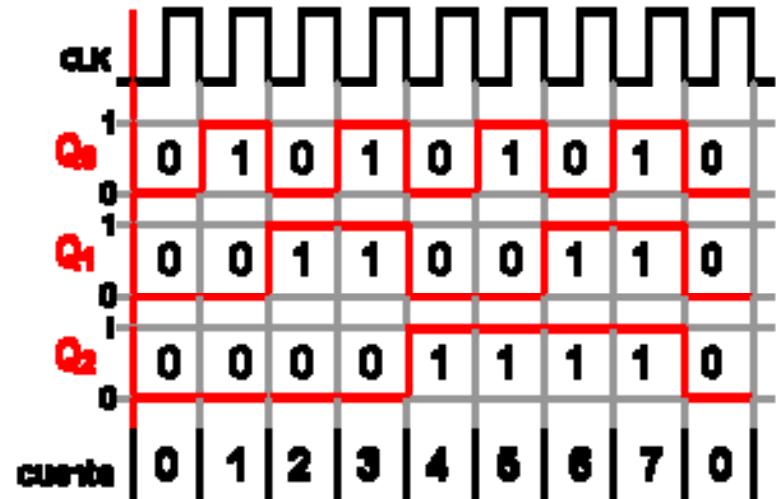

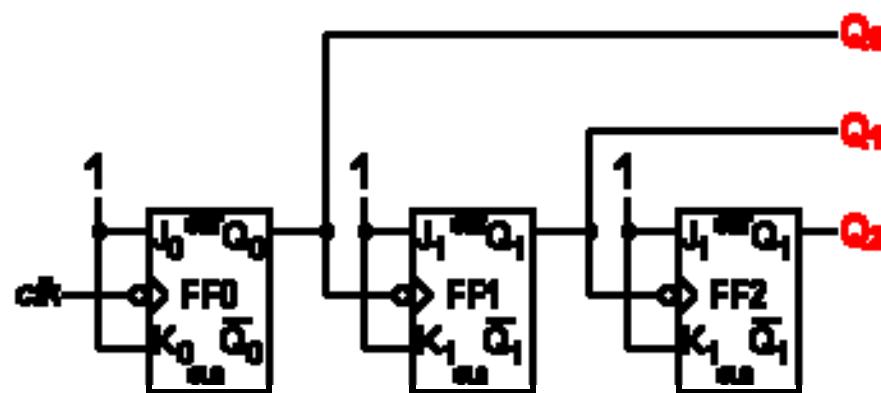

# Contadores Asincrónicos

# Contadores Asincrónicos

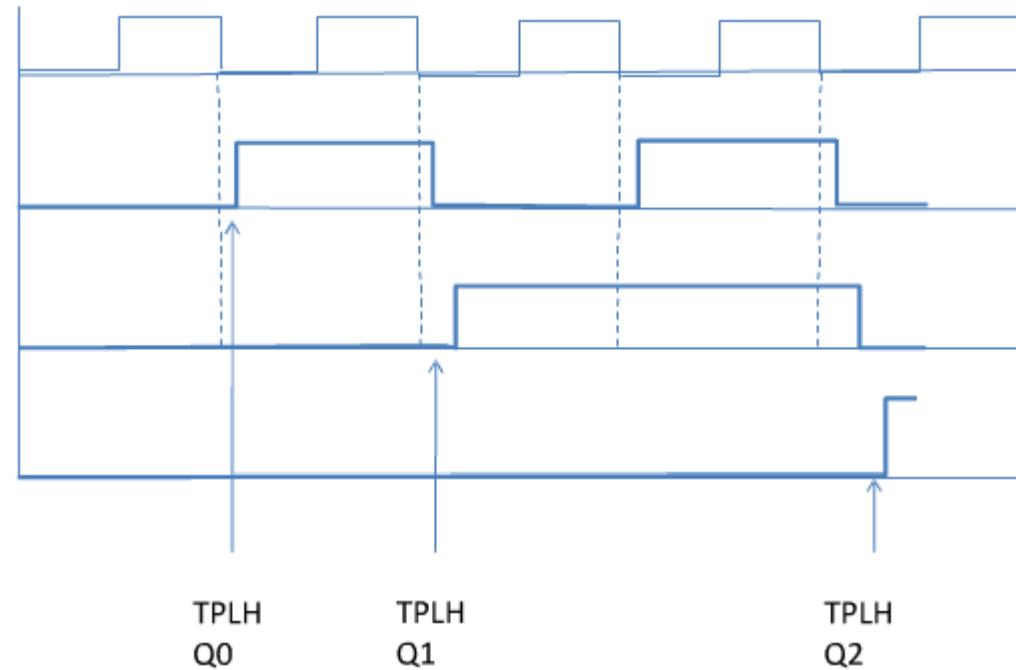

El principal problema que tienen los contadores asincrónicos es el retardo de propagación que se suma en cada etapa. Esto limita la máxima frecuencia de operación.

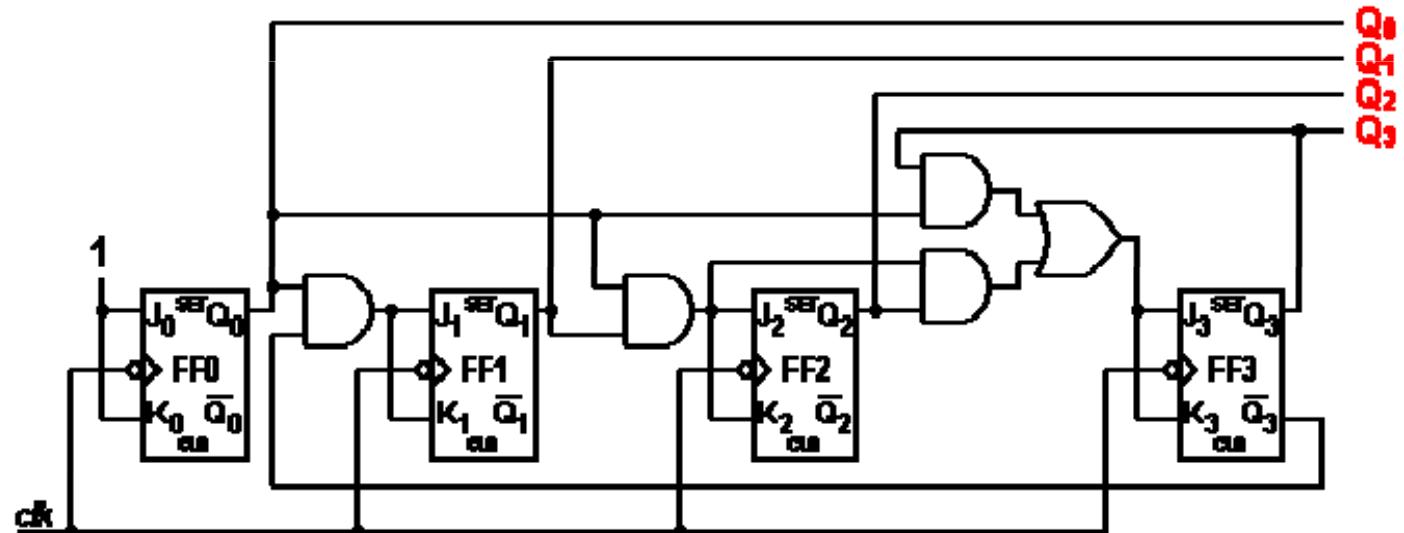

# Contadores Sincrónicos

Todos los Flip-Flops evolucionan con la misma señal de reloj. Una lógica combinacional decide si la próxima etapa debe cambiar de estado o no.

Contador decimal 0 a 9

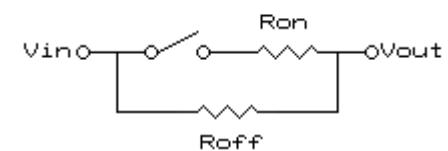

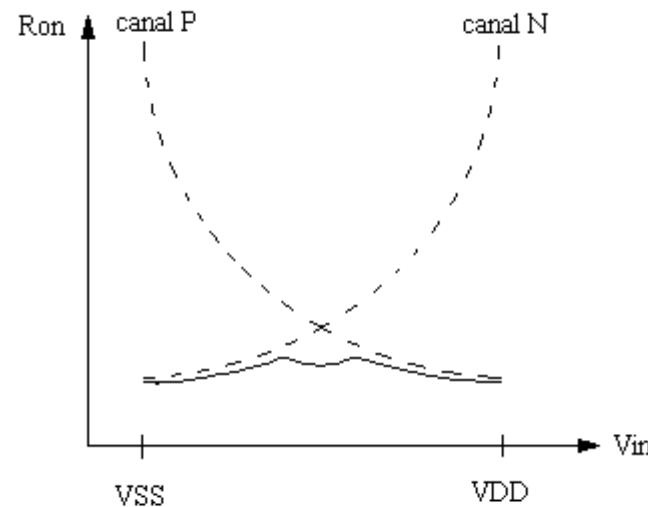

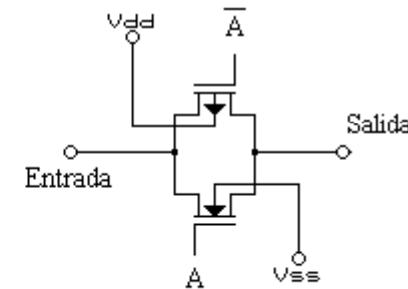

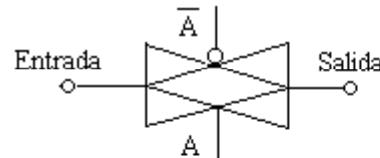

# Llaves Analógicas

- Formadas por 2 MOS en paralelo; un P y un N.

- La resistencia equivalente entre Entrada y Salida es el paralelo de ambas resistencias de canal.

- Permiten transmitir señales analógicas.

- Se las usa como llaves selectoras o multiplexores

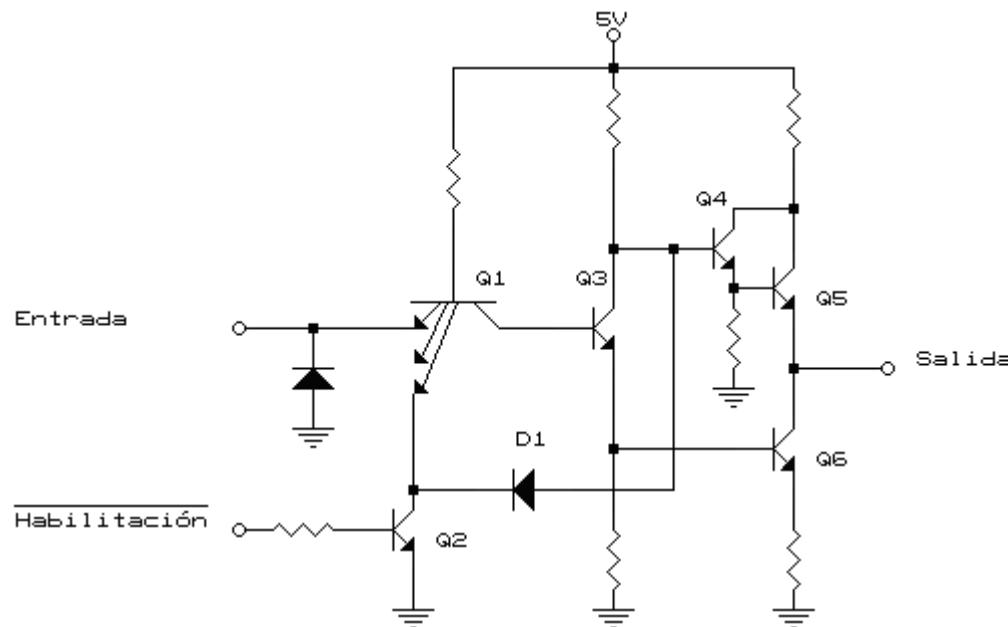

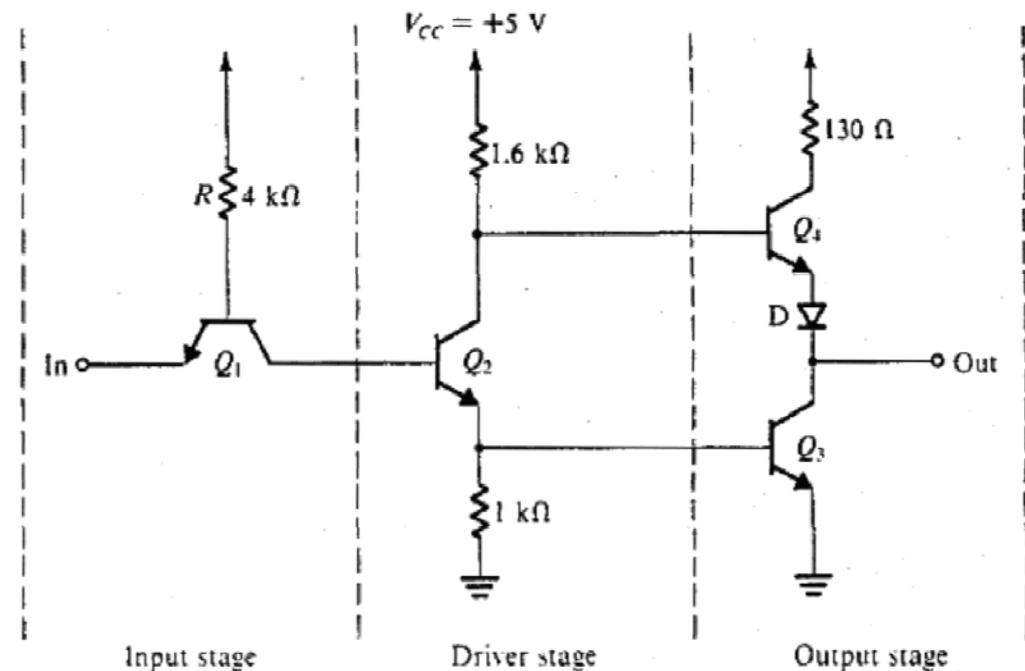

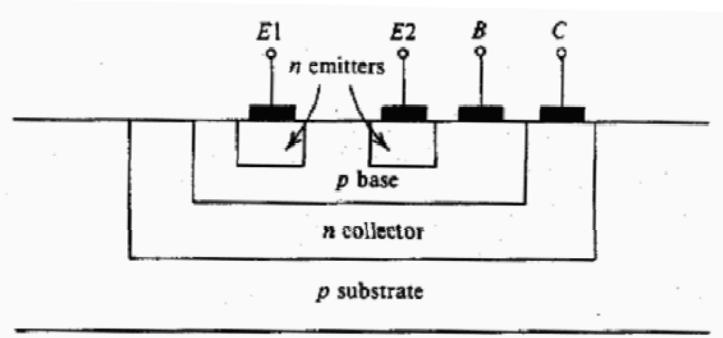

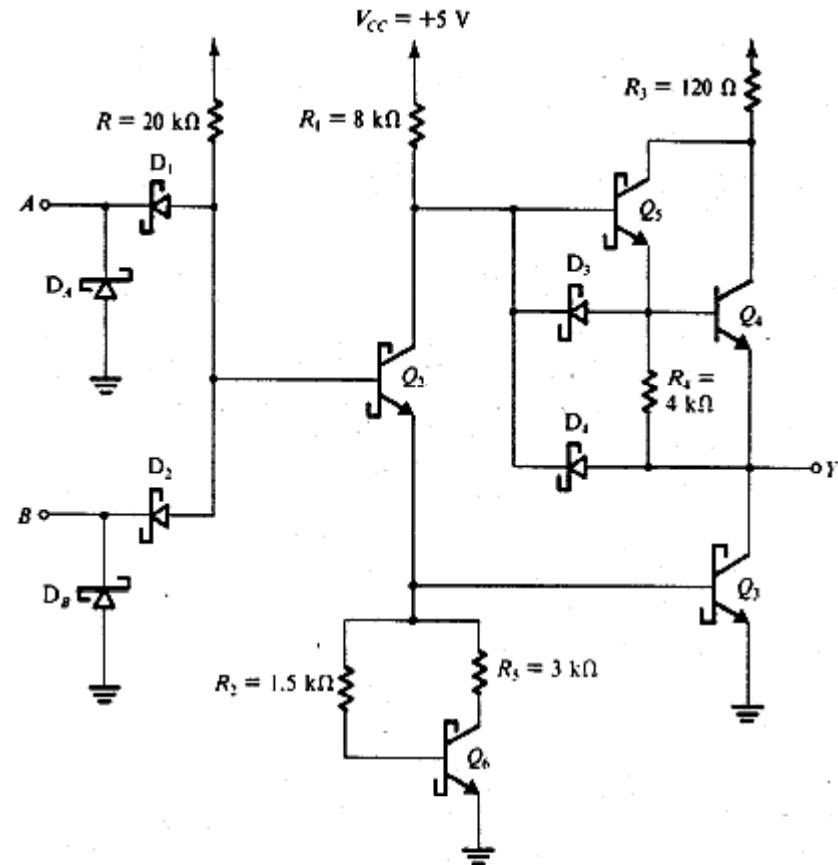

# Lógica TTL

- Basada en transistores BJT

- Buena velocidad

- Gran consumo

- Área importante

- Buena capacidad de corriente

- El consumo de entrada es diferente para un '0' que para un '1'.

- $V_{CC} = 5V$

# Lógica TTL

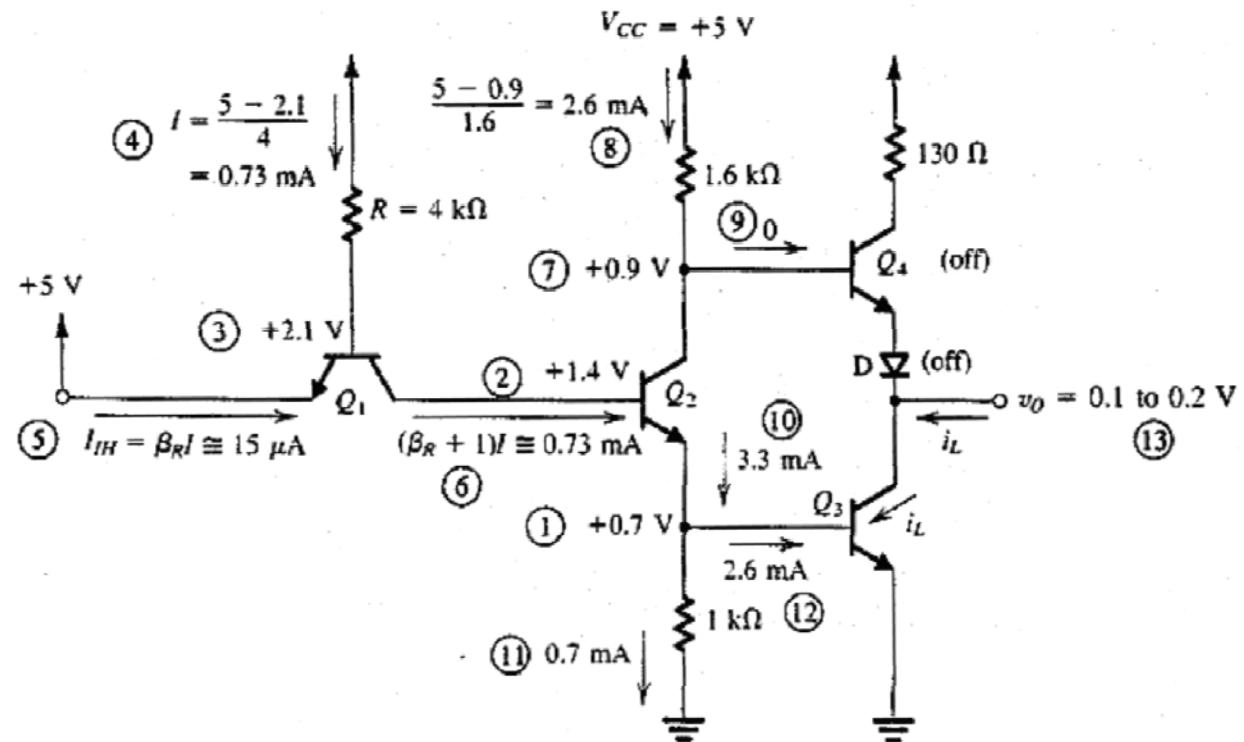

- Entrada en '1'.

# Lógica TTL

- Entrada en '0'

# Lógica TTL

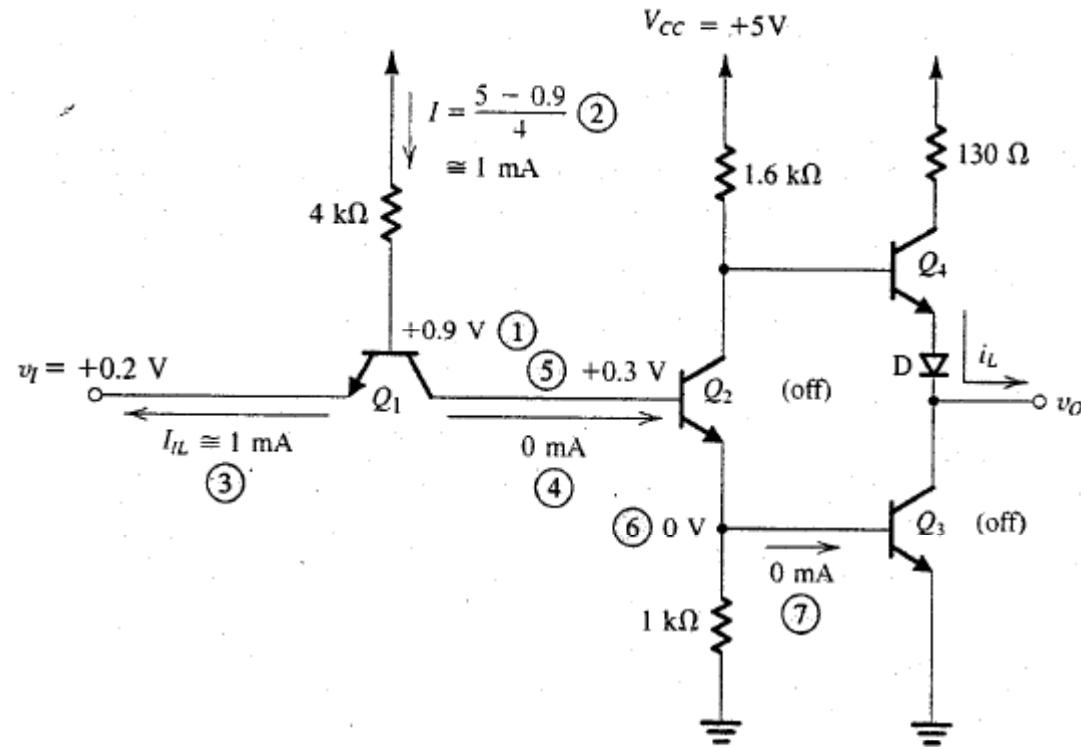

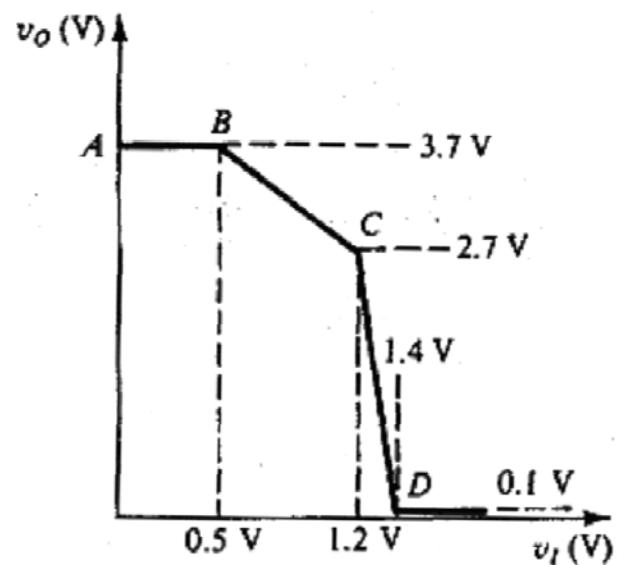

- Características de transferencia

# Lógica TTL

$$NM_H = V_{OH} - V_{IH} = 0.4 \text{ V}$$

$$NM_L = V_{IL} - V_{OL} = 0.4 \text{ V}$$

- Niveles lógicos y corrientes

|                 |                                | SN5400 |     |      | SN7400 |     |      | UNIT |

|-----------------|--------------------------------|--------|-----|------|--------|-----|------|------|

|                 |                                | MIN    | NOM | MAX  | MIN    | NOM | MAX  |      |

| V <sub>CC</sub> | Supply voltage                 | 4.5    | 5   | 5.5  | 4.75   | 5   | 5.25 | V    |

| V <sub>IH</sub> | High-level input voltage       | 2      |     |      | 2      |     |      | V    |

| V <sub>IL</sub> | Low-level input voltage        |        |     | 0.8  |        |     | 0.8  | V    |

| I <sub>OH</sub> | High-level output current      |        |     | -0.4 |        |     | -0.4 | mA   |

| I <sub>OL</sub> | Low-level output current       |        |     | 16   |        |     | 16   | mA   |

| T <sub>A</sub>  | Operating free-air temperature | -55    | 125 |      | 0      | 70  |      | °C   |

| PARAMETER        | TEST CONDITIONS†                                                          | SN5400 |      |      | SN7400 |      |      | UNIT |

|------------------|---------------------------------------------------------------------------|--------|------|------|--------|------|------|------|

|                  |                                                                           | MIN    | TYP§ | MAX  | MIN    | TYP§ | MAX  |      |

| V <sub>IK</sub>  | V <sub>CC</sub> = MIN, I <sub>I</sub> = -12 mA                            |        |      | -1.5 |        |      | -1.5 | V    |

| V <sub>OH</sub>  | V <sub>CC</sub> = MIN, V <sub>IL</sub> = 0.8 V, I <sub>OH</sub> = -0.4 mA | 2.4    | 3.4  |      | 2.4    | 3.4  |      | V    |

| V <sub>OL</sub>  | V <sub>CC</sub> = MIN, V <sub>IH</sub> = 2 V, I <sub>OL</sub> = 16 mA     |        | 0.2  | 0.4  |        | 0.2  | 0.4  | V    |

| I <sub>I</sub>   | V <sub>CC</sub> = MAX, V <sub>I</sub> = 5.5 V                             |        |      | 1    |        |      | 1    | mA   |

| I <sub>IH</sub>  | V <sub>CC</sub> = MAX, V <sub>I</sub> = 2.4 V                             |        |      | 40   |        |      | 40   | µA   |

| I <sub>IL</sub>  | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.4 V                             |        |      | -1.6 |        |      | -1.6 | mA   |

| I <sub>OS¶</sub> | V <sub>CC</sub> = MAX                                                     | -20    | -55  |      | -18    | -55  |      | mA   |

| I <sub>CCH</sub> | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0 V                               |        | 4    | 8    |        | 4    | 8    | mA   |

| I <sub>CCL</sub> | V <sub>CC</sub> = MAX, V <sub>I</sub> = 4.5 V                             |        | 12   | 22   |        | 12   | 22   | mA   |

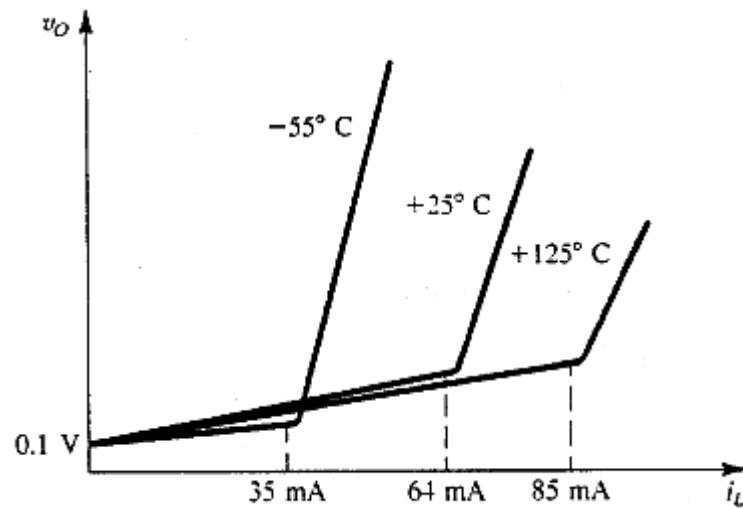

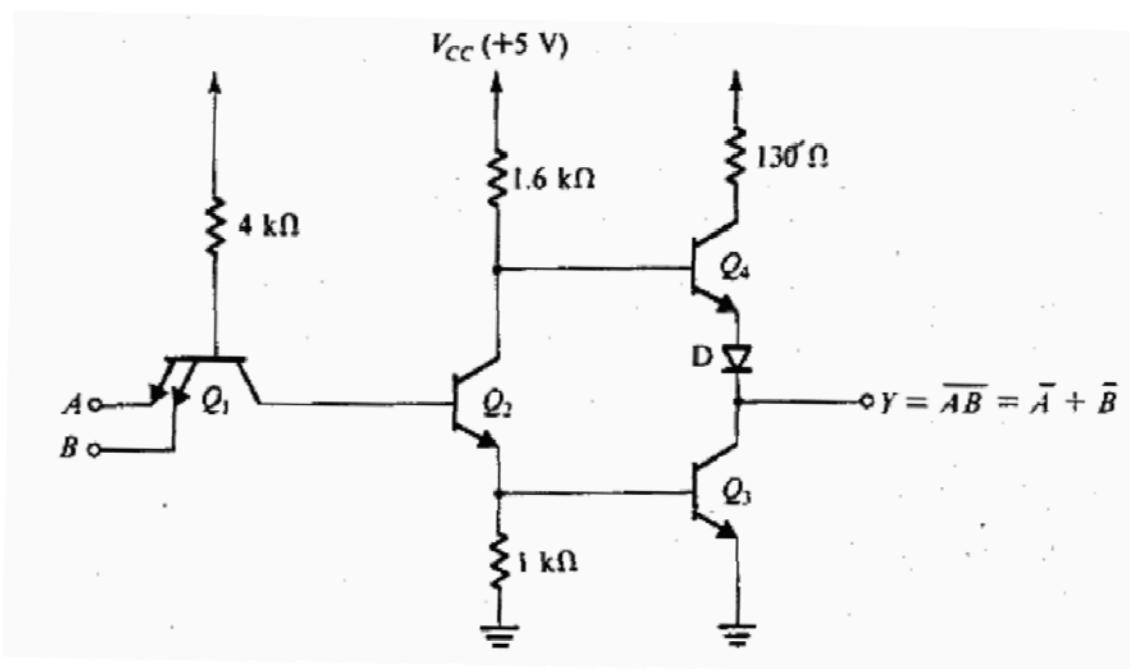

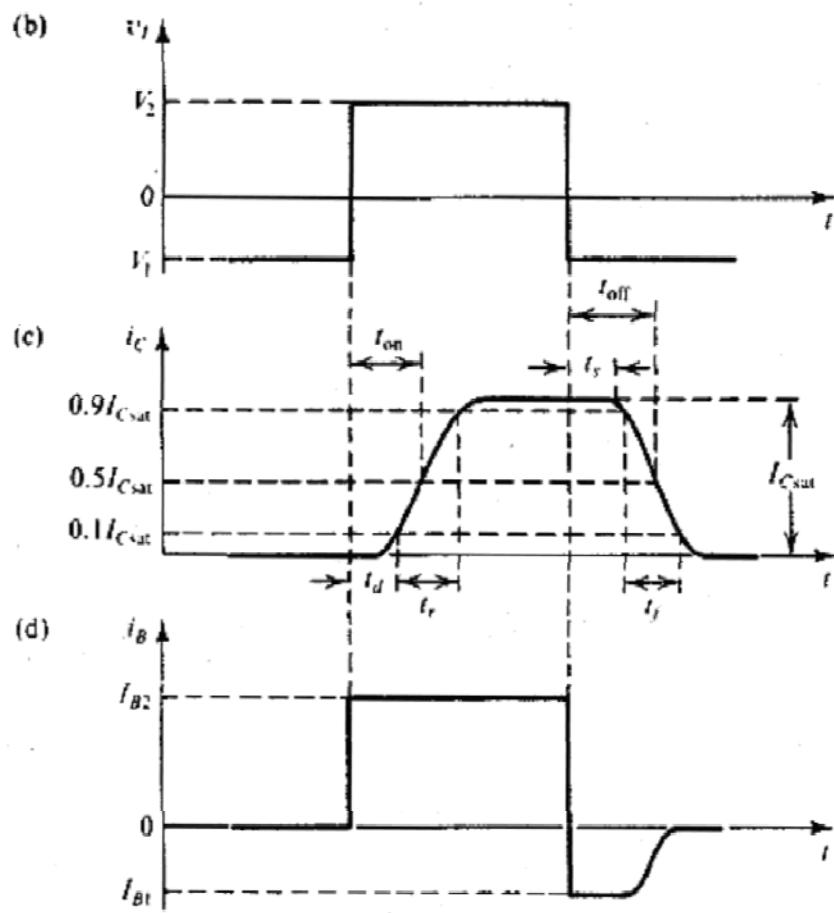

# Lógica TTL

- TTL NAND 2 entradas

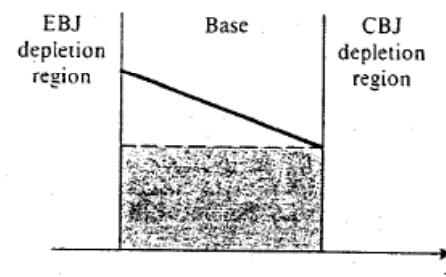

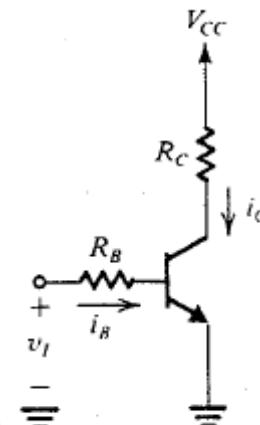

# BJT en commutación

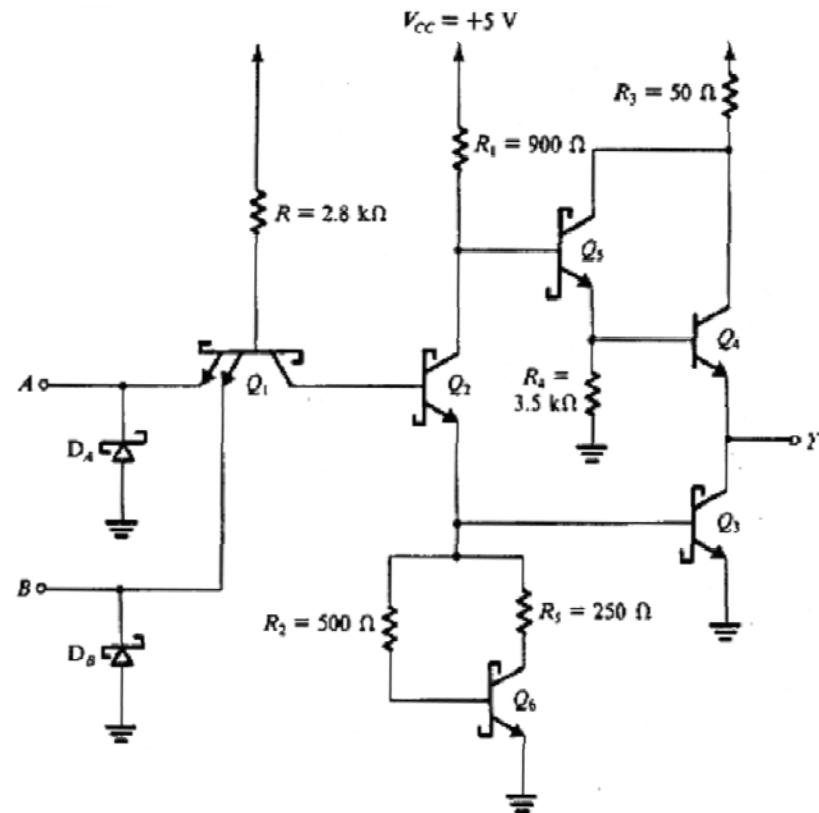

# Schottky TTL (S)

- Previene la saturación de los BJT colocando diodos Schottky en las junturas BC. De esta forma mejora la performance en velocidad de operación.

- El diodo de salida se reemplaza por una configuración Darlington.

- La resistencia de 1K se reemplaza por un Pull-Down activo.

- Aumenta el consumo

Introducción a la Electrónica

# Low Power Schottky TTL (LS)

- Similar a la S, salvo que se reduce la velocidad y la disipación de potencia.

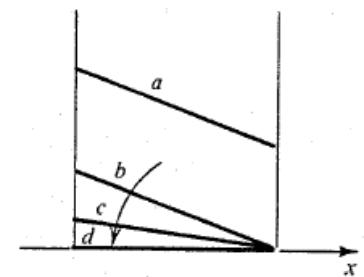

# Familias TTL

Table 14.1 PERFORMANCE COMPARISON OF TTL FAMILIES

|            | Standard TTL<br>(Series 74) | Schottky TTL<br>(Series 74S) | Low-Power<br>Schottky TTL<br>(Series 74LS) | Advanced<br>Schottky TTL<br>(Series 74AS) | Advanced Low-Power<br>Schottky TTL<br>(Series 74ALS) |

|------------|-----------------------------|------------------------------|--------------------------------------------|-------------------------------------------|------------------------------------------------------|

| $t_P$ , ns | 10                          | 3                            | 10                                         | 1.5                                       | 4                                                    |

| $P_D$ , mW | 10                          | 20                           | 2                                          | 20                                        | 1                                                    |

| $DP$ , pJ  | 100                         | 60                           | 20                                         | 30                                        | 4                                                    |

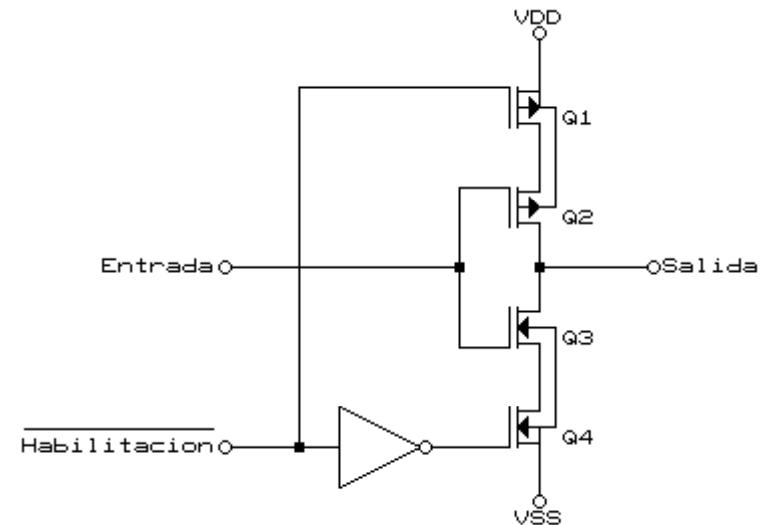

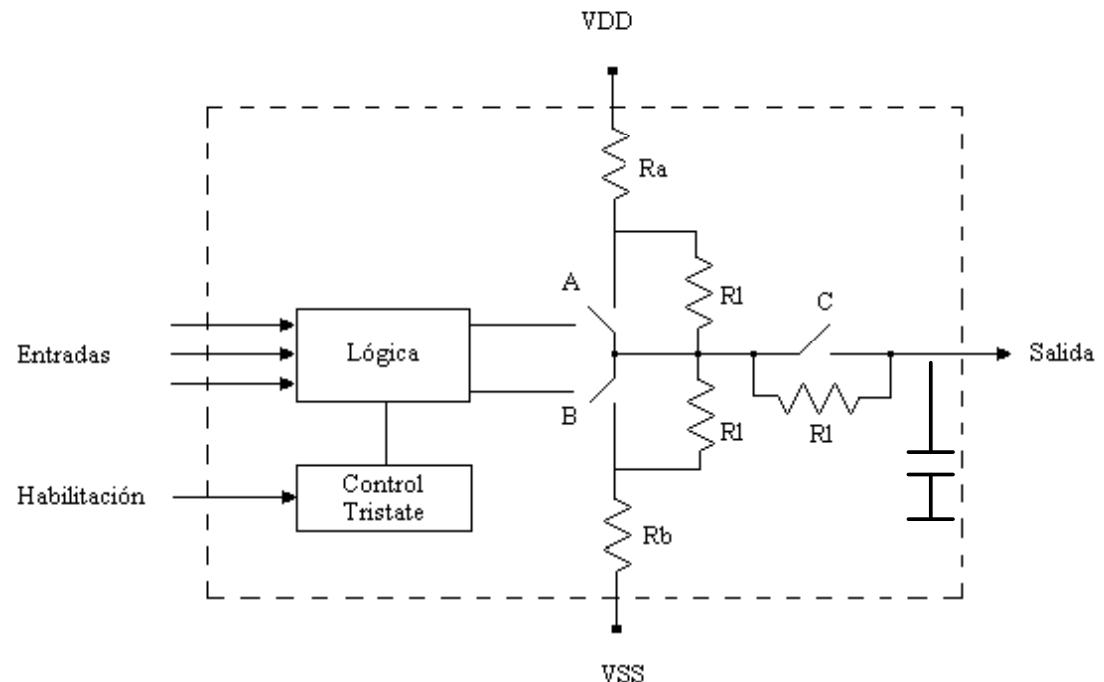

# Lógica de 3º estado

- Se agrega un estado de alta impedancia en el cual la compuerta no entrega ningún valor lógico.

- Se utiliza en canales (buses) donde confluyen diversas compuertas capaces de establecer el valor lógico; por ejemplo bus de datos de un microprocesador.

# Lógica de 3º estado